# TRANSISTORES DE EFECTO DE CAMPO DE COMPUERTA AISLADA DE POTENCIA (POWER MOSFET)

Dadas las limitaciones de los BJTs de potencia, surge la necesidad de desarrollar componentes de otra tecnología que puedan superarlas.

Una de las alternativas es desarrollar un dispositivo tipo transistor de efecto de campo de compuerta aislada que opere solo con portadores mayoritarios y que sea capaz de manejar corrientes significativas (PowerMOSFET), superando las limitaciones de los MOSFETs convencionales o de "pequeña señal"

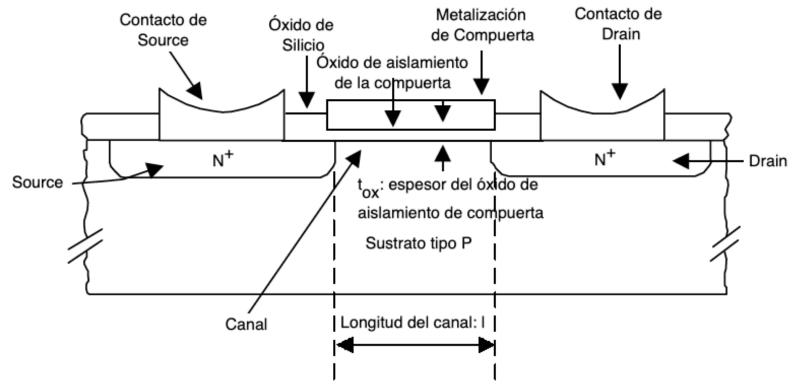

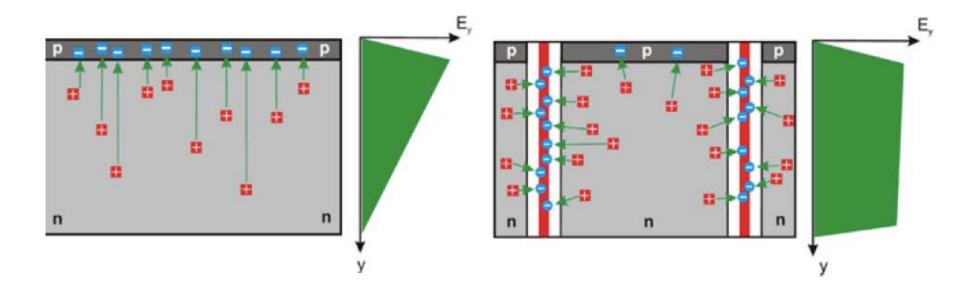

Estructura de un transistor de efecto de campo de Compuerta aislada (MOSFET) convencional

En un MOSFET convencional de propósito general la corriente principal, I<sub>DS</sub>, se desplaza en un "canal de conducción horizontal" que es una franja superficial muy poco profunda, lo que dificulta operar con altas corrientes de carga.

Sin embargo el MOSFET presenta dos características que lo hacen interesante como base de un dispositivo electrónico de control de potencia:

- 1.-Su estado (conducción o corte) está controlado por la tensión acumulada en el condensador equivalente G-S, lo que minimiza la corriente de control necesaria.

- 2.-No presenta deriva térmica, por lo que en principio es posible conectar N MOSFETs en paralelo para manejar una corriente N veces mayor.

#### Solución:

Modificar la topología básica del MOSFET para que la corriente principal tenga un recorrido esencialmente vertical, lo que unido a la inexistencia del problema de "corrida térmica", permitirá producir una estructura compuesta en la que la corriente de trabajo a nivel de los terminales del dispositivo sea la suma de las n corrientes elementales conducidas por cada uno de los n MOSFETs elementales idénticos conectados fabricados simultáneamente empleando las técnicas de producción de circuitos integrados de alto nivel de integración (LSI) y conectados en paralelo por las metalizaciones de Drenador (D, Drain), Surtidor (S, Source) y Compuerta (G, Gate).

## I.-PowerMOSFETs de primera generación.

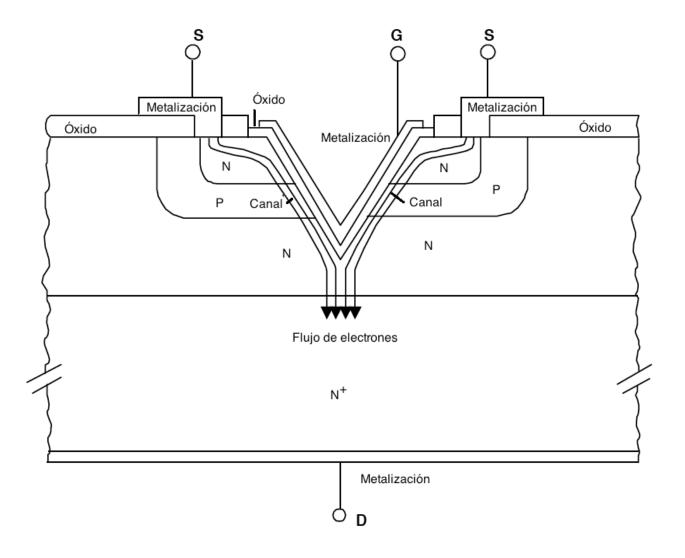

Para logra esto, inicialmente la compañía Siliconix propuso una estructura basada en un sustrato tipo N en el cual se difundía una serie paralela de inclusiones longitudinales tipo P y, centrada en cada una de estas inclusiones tipo P, se creaba otra inclusión tipo N; a continuación en cada una de estas estructuras NPN se abría por ataque químico un surco en "V" ("trinchera") escavado de forma que cortaba completamente la zona N superficial y la P intermedia, penetrando en la N profunda de cada inclusión; las paredes de los surcos se cubrían con una capa aislante de óxido de Si  $(SiO_2)$ , y sobre esta se metalizaba un electrodo de Compuerta; la estructura se repetía como una serie de surcos longitudinales equi-espaciados sobre toda la superficie del chip los electrodos.

Los electrodos de Compuerta de todas las trincheras se conectaban en paralelo formando la "Compuerta" del MOSFET. La cara inferior del cristal N se metalizaba como un contacto común de Drenador, y las todas las inclusiones tipo N se conectaban en paralelo formando el electrodo de Surtidor; el arreglo de las Compuertas básicas controlaba la formación de canales básicos en cada una de las regiones P a todo lo largo de ambos lados de cada una de las trincheras.

Corte vertical de un PowerMOSFET de trinchera abierta en V (V-MOS).

En estos MOSFETs, encapsulados en formato TO-5, se alcanzaban corrientes de hasta 5A, pero la concentración de corriente en el vértice de la "V" durante las conmutaciones producía calentamientos localizados, tensionando mecánicamente la estructura del cristal, causando eventualmente la "fatiga" del material cristalino, lo que podía generar fallos destructivos.

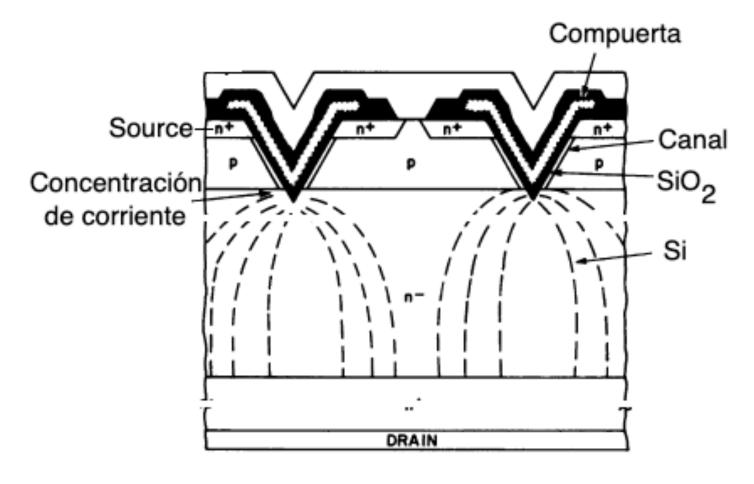

Esquema de la concentración de portadores en el vértice de una trinchera tipo "V".

Para tratar de resolver el problema de la concentración de tensiones mecánicas en los vértices, se desarrollaron versiones en "V truncada", en la que la trinchera tenía un fondo plano, en vez del vértice.

Las tensiones mecánicas se reducían, aunque no desaparecían, concentrándose ahora en los ángulos de unión entre las paredes y el fondo de la trinchera.

Esto reducía el problema de la concentración de corriente, pero seguía existiendo el de un proceso de fabricación complejo para depositar las capas de óxido y de metalización en las trincheras.

Corte vertical de un PowerMOSFET de trinchera abierta en "V-truncada" (U-FET).

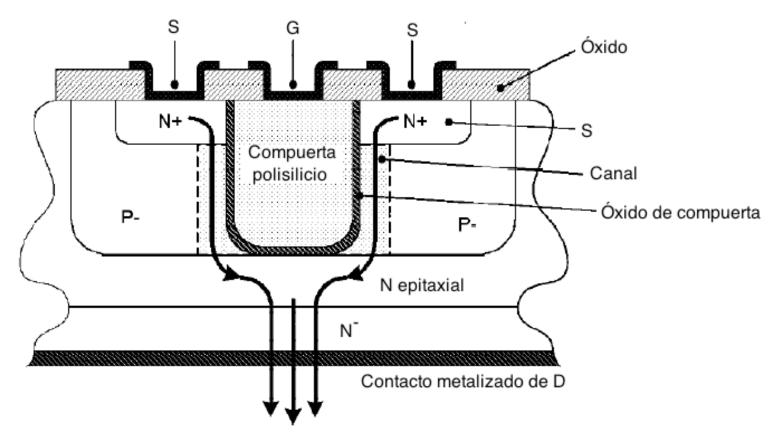

Para solucionar el problema se propuso una estructura de trinchera mas abierta, en forma de "U", haciendo que los canales fueran totalmente verticales y eliminando los vértices donde se concentraba la corriente, y luego una de "trinchera enterrada", en la cual la "U" se rellenaba con poli-silicio para formar la Compuerta, lo cual eliminaba la necesidad de metalizar los lados de la trinchera.

Corte vertical de un PowerMOSFET de Compuerta enterrada (trinchera cerrada).

### II.-PowerMOSFETs de segunda generación.

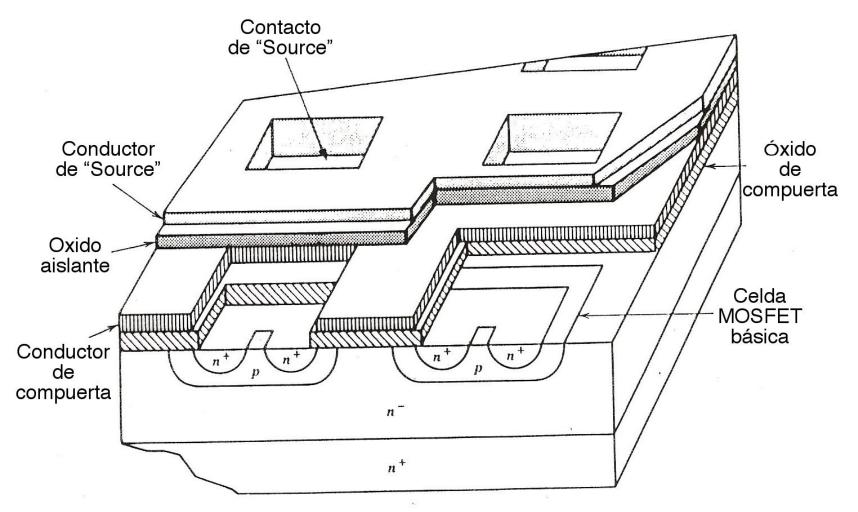

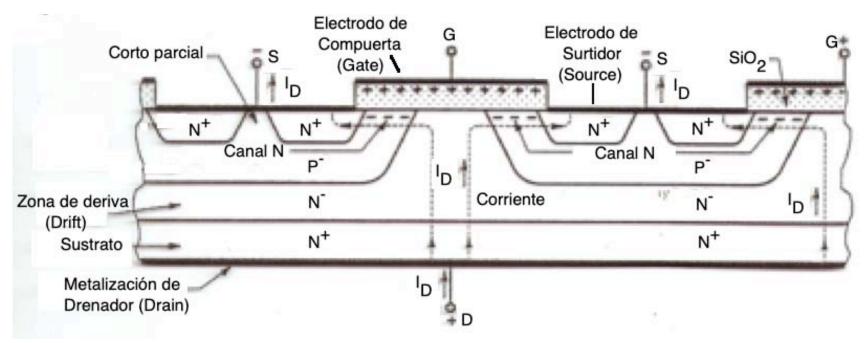

En la segunda generación de PowerMOSFETs, las estructuras de trinchera, difíciles de producir sin defectos, han sido reemplazadas por estructuras tipo "isla", que no requieren abrir surcos para las trincheras.

La configuración en isla tiene la ventaja adicional de que es totalmente compatible con la tecnología de fabricación de circuitos integrados LSI y VLSI, por lo que el desarrollo ha sido significativamente simplificado.

Aunque los dispositivos de trinchera fueron los primeros en llegar al mercado, la estructura de islas es más fácil de fabricar y no presenta esquinas que concentran los campos eléctricos y aumentan la posibilidad de falla, así que los de estructura de isla han reemplazado a los de trinchera.

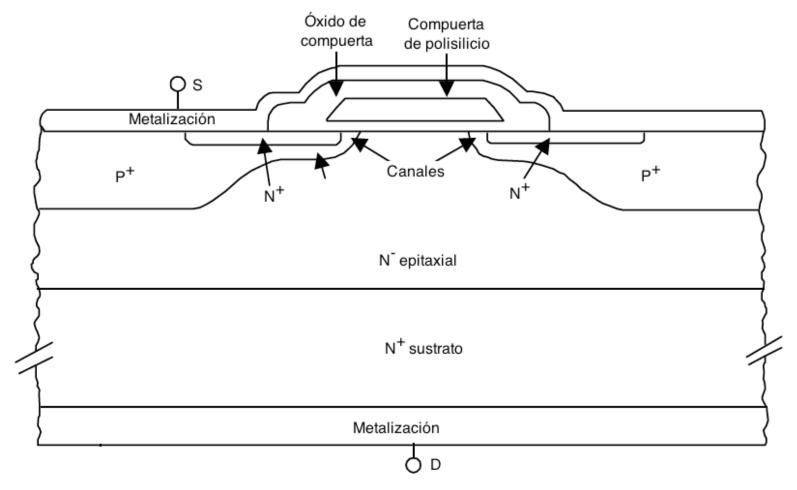

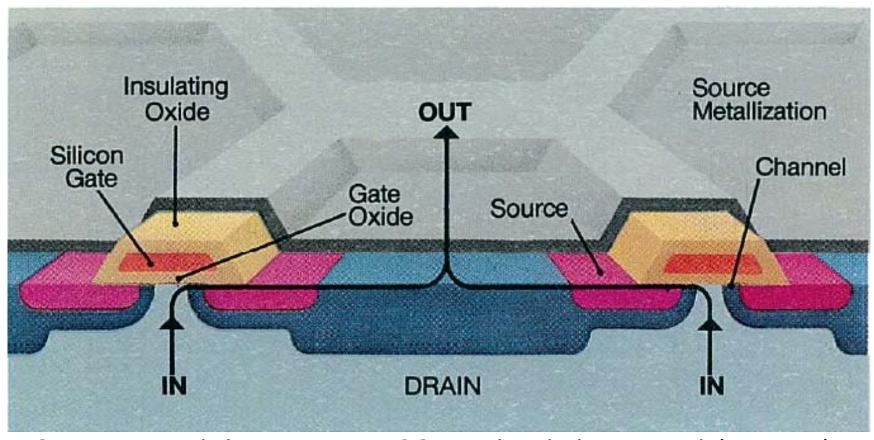

Corte vertical de una celda básica de conducción en un transistor de efecto de campo de potencia de estructura de isla (PowerMOSFET actual).

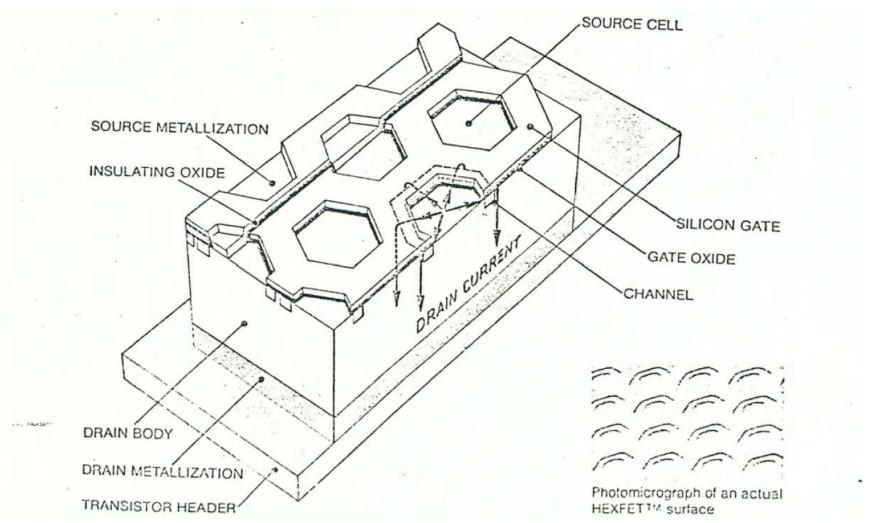

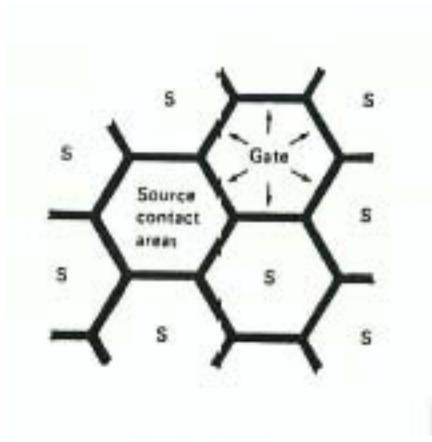

La estructura tipo isla fue comercializada inicialmente por International Rectifier (I.R.), compañía que patentó un diseño con islas hexagonales, produciendo y promocionando sus PowerMOSFETs bajo su marca registrada "HEXFET"; otros fabricantes presentaron posteriormente configuraciones similares, pero con islas cuadradas.

En ambos casos cada isla forma un MOSFET básico, y todas las islas están conectadas en paralelo para formar un arreglo que actúa como un elemento único.

Corte vertical de un PowerMOSFET de isla hexagonal (HEXFET), cortesía International Rectifier.

Estereometría de una sección de un HEXFET (cortesía International Rectifier)

Arreglo de los contactos de S y G en un PowerMOSFET de tipo "hexagonal" (HEXFET). Cortesía International Rectifier.

Corte de un POWERMOSFET tipo TFET (islas cuadradas).

En todas las estructuras tipo isla la circulación de la corriente tiene un tramo vertical, del electrodo de Drenador al centro de la isla, y otro horizontal a través del canal que se forma en toda la periferia de la isla.

Esquema de voltajes y corrientes durante la conducción en un POWERMOSFET tipo isla.

El esquema de la trayectoria de la corriente en cada isla tiene forma de "T", de allí el nombre "T-FET usado por ciertos fabricantes.

Aunque la estructura de islas de la segunda generación eliminó la mayoría de las limitaciones de los PowerMOSFETs de primera generación, estos dispositivos estaban intrínsicamente limitados en su capacidad de operar simultáneamente con altas corrientes y altas tensiones de bloqueo.

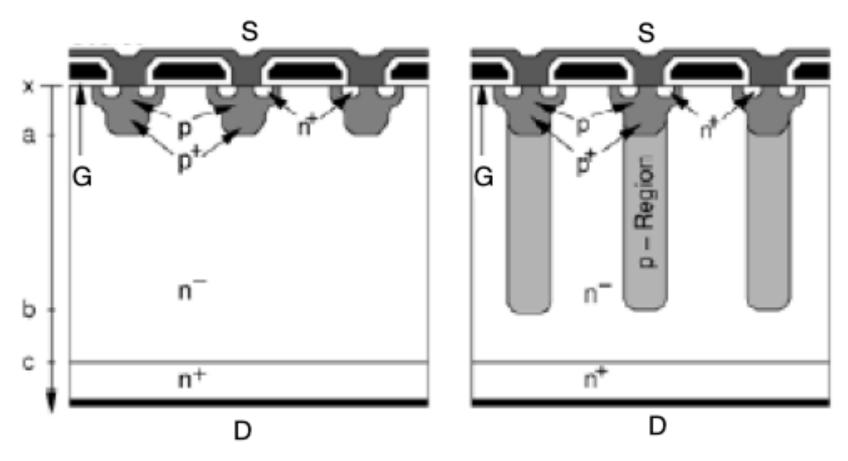

# III.-PowerMOSFETs de tercera generación.

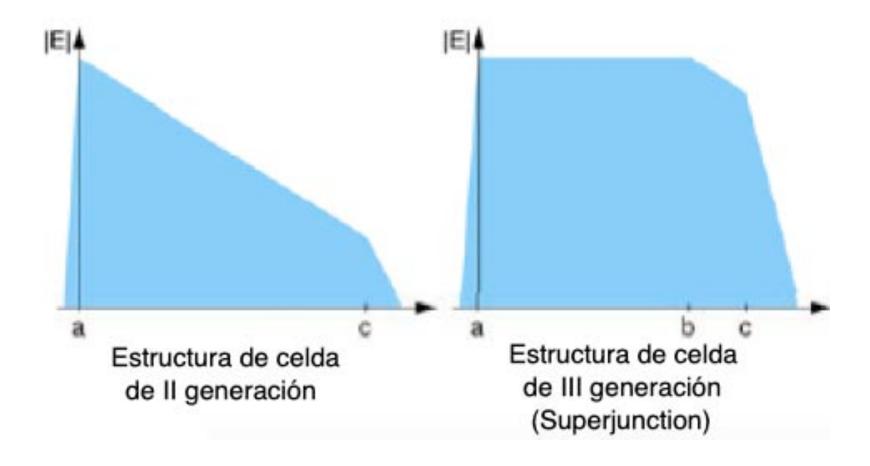

Para superar las limitaciones que los PowerMOSFET de segunda generación tienen para operar simultáneamente a altas corrientes y altos voltajes de bloqueo, la compañía Infineon introdujo en 1999 los PowerMOSFETs de tercera generación o Superjunction PowerMOSFETs, comercializados como "CoolMOS", capaces de operar a tensiones de bloqueo de 500V y 1000V.

En estos dispositivos la estructura básica de los PowerMOSFETs de segunda generación se modifica introduciendo una nueva región con dopaje P- como continuación de las islas P que caracterizan a la segunda generación. Esto cambia la distribución del campo eléctrico, lo que modifica la relación entre la resistencia en conducción y la tensión de bloque, permitiendo que los Superjunction MOSFETs operen a niveles de tensión y potencia similares a las de los IGBTs.

Comparación entre las estructuras de celda de los PowerMOSFETs de II<sup>a</sup> generación (izquierda) y los PowerMOSFETs de III<sup>a</sup> generación tipo Superjunction (derecha).

Cortesía Infineon.

Comparación entre las distribución del campo eléctrico de las estructuras de celda de los PowerMOSFETs de II<sup>a</sup> generación (izquierda) y los PowerMOSFETs de III<sup>a</sup> generación tipo Superjunction (derecha). Cortesía Infineon.

Los desarrollos continúan, y la misma compañía Infineon ha introducido una nueva configuración, comercializada bajo el nombre genérico de "OptiMOS", en la que las columnas tipo P<sup>-</sup> de los Superjunction se reemplazan con las llamadas "placas de campo" ("field plates") que permiten una modificación del perfil del campo eléctrico similar a la lograda con las inclusiones P<sup>-</sup>, pero a un costo menor. Las placas de campo se construyen en base a trincheras verticales en las cuales se deposita un electrodo aislado mediante dos capas de SiO<sub>2</sub>; el arreglo de electrodos así creado se conecta por parejas uno al terminal de Surtidor y el otro a la compuerta de polisilicio.

Esta tecnología de fabricación es aplicable a dispositivos con tensiones de bloqueo del orden de los 300V y produce PowerMOSFEts que operan con pérdidas en conducción menores a los equivalentes de II<sup>a</sup> generación.

Comparación de los perfiles de campo en una estructura PowerMOSFET de II<sup>a</sup> generación y una estructura PowerMOSFET de III<sup>a</sup> generación tipo OptiMOS. Cortesía Infineon.

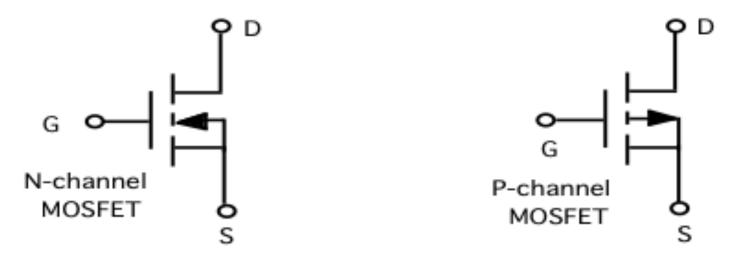

## PowerMOSFETs tipo N y tipo P

Las configuraciones consideradas producen MOSFETs tipo N, ya que los portadores que se mueven en el canal son tipo N (electrones).

Si en cualquiera de las posibles estructuras de un PowerMOSFET los dopados se intercambian, reemplazando las zonas tipo P por zonas tipo N y viceversa, el resultado es un transistor MOSFET de potencia tipo P, en el cual los portadores que se desplazan en el canal son tipo P ("huecos").

Las características generales del MOSFET de potencia tipo P son similares a las del MOSFET de potencia tipo N, salvo en lo referente a la polaridad de las señales de encendido y apagado aplicadas a la compuerta y, lo que es mas importante, a la movilidad de los

portadores de la corriente, huecos en este caso, que es menor, lo cual significa que, en igualdad de condiciones de voltaje y corriente, y con chips de tamaño y estructura equivalentes, la velocidad de conmutación será menor en el MOSFET de potencia tipo P.

Debido a esto los MOSFET de potencia tipo P son poco usados, y no serán considerados específicamente en estas notas.

Símbolo circuital de los PowerMOSFETs de canal N (izquierda) y de canal P (derecha).

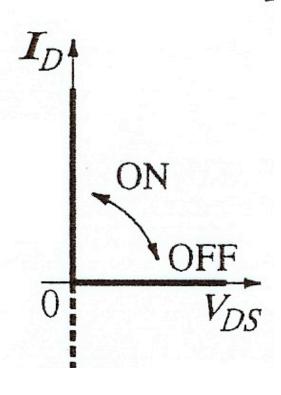

#### EL POWERMOSFET COMO CONMUTADOR DE POTENCIA.

Idealmente se desearía que el PowerMOSFET cumpliese con la siguiente característica  $I_{DS}/V_{DS}$

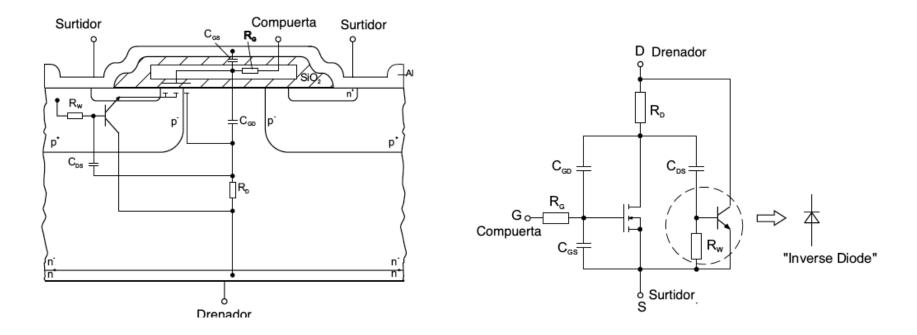

En la realidad la estructura implementada en cualquiera de las tres generaciones de PowerMOSFETs es bastante complicada y al caracterizarla se pueden individualizar una gran cantidad de elementos circuitales básicos distribuidos en diversas partes de la estructura del cristal semiconductor que influyen en la operación y modifican las características ideales deseadas.

En general la mayoría de estos elementos secundarios son "parásitos", ya que su efecto degrada el comportamiento deseado.

Elementos circuitales definibles en un PowerMOSFET (izquierda) y circuito equivalente (derecha). Cortesia Semikron.

Los elementos circuitales definibles en la estructura de un PowerMOSFET se puede agrupar en cuatro categorías:

- 1.-Resistencias que aumentan las pérdidas en conducción.

- 2.-Transistores BJT y JFET parásitos que pueden entrar en conducción interfiriendo con la operación controlada del MOSFET.

- 3.-Capacitores que deben ser cargados y descargados durante las conmutaciones, introduciendo los consiguientes retardos.

- 4.-Diodos que conectan el terminal de Surtidor al de Drenador en anti-paralelo con cada MOSFET elemental.

# Efectos de los elementos parásitos sobre el comportamiento del PowerMOSFET

- 1.- El JFET restringe el flujo de corriente cuando la región de empobrecimiento de los dos diodos se extiende al aumentar la tensión de Drenador (Drain) lo que aumenta las pérdidas en conducción.

- 2.-El BJT puede producir encendidos indeseados y ruptura prematura.

- 3.- El conjunto de resistencias hace que, en igualdad de condiciones en lo relativo a superficie del dispositivo y corriente y tensión de operación, la caída en conducción en un PowerMOSFET es mayor que la caída en un BJT de potencia en diseños donde el voltaje de ruptura de los dispositivos es mayor a 200 V.

4.-El diodo anti-paralelo elimina la posibilidad de bloquear tensiones inversas.

Normalmente este diodo no se considera un elemento parásito sino un componente deseado, dado que es útil en muchos circuitos conversores, aunque como no puede ser optimizado sin afectar otros parámetros de mayor interés en el PowerMOSFET, su velocidad de conmutación no es óptima, por lo que a veces es preciso bloquear su acción mediante un diodo en serie con el MOSFET, y colocando un diodo rápido, preferiblemente Schottky en anti-paralelo con el arreglo PowerMOSFET-diodo en serie.

En estas aplicaciones el diodo anti-paralelo intrínseco efectivamente resulta un elemento parásito indeseable.

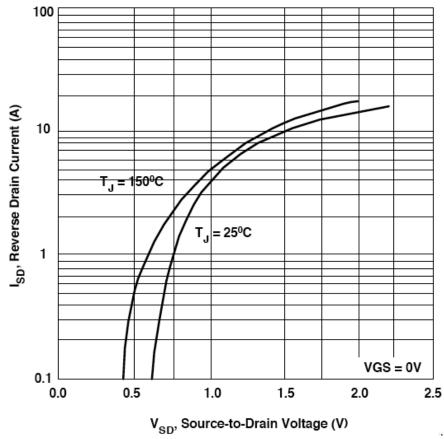

Curvas corriente/voltaje típicas del diodo de conducción inversa asociado con la estructura de un PowerMOSFET.

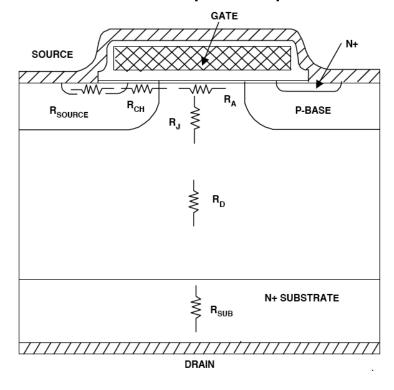

Elementos que componen la resistencia de encendido,  $R_{DS(on)}$ , de un transistor de efecto de campo de potencia (PowerMOSFET)

$$R_{DS(on)} = R_S + R_{Ch} + R_A + R_j + R_D + R_{sus} + R_m$$

R<sub>DS(on)</sub>: Resistencia en conducción, medida entre los terminales D y S del dispositivo encapsulado

R<sub>s</sub>: resistencia de la región de Surtidor (Source)

R<sub>ch</sub>: Resistencia del canal (channel)

R<sub>A</sub>: resistencia de la región de acumulación

R<sub>J</sub>: Componente resistivo del JFET residual

R<sub>D</sub>: Resistencia de la zona de deriva (drift)

R<sub>sub</sub>: Resistencia del substrato

R<sub>m</sub>: Resistencia acumulada de las metalizaciones y conductores metálicos.

En general en un PowerMOSFET la relación entre la caída resistiva que aparece entre los terminales de Drenador y Surtidor cuando el dispositivo está encendido y el valor de la tensión de bloqueo, V<sub>DS</sub>, de acuerdo con la relación:

$$R_{DS} = KV_{DS}^e$$

Donde K es un factor empírico que depende del tamaño del dispositivo y el factor e depende del proceso de fabricación.

El factor K tiene un valor de 8,3\*10<sup>-9</sup> A<sup>-1</sup> por cm<sup>2</sup> de superficie del chip.

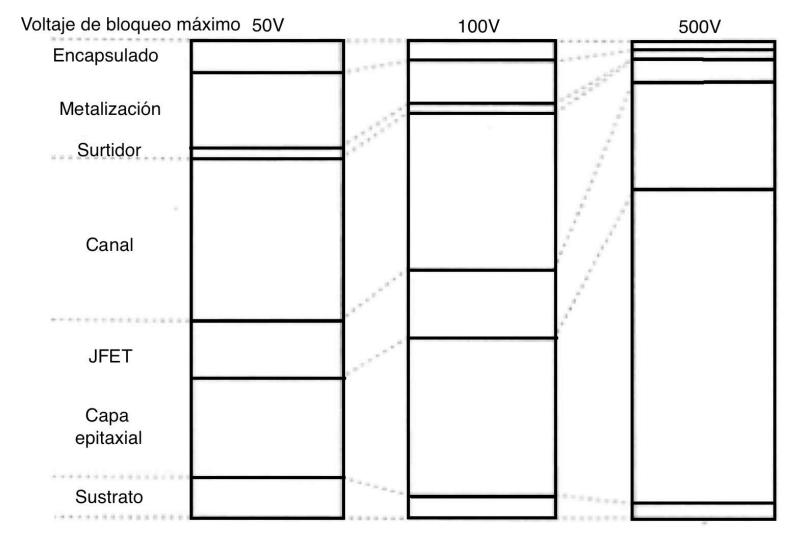

En los PowerMOSFET de las dos primeras generaciones el factor exponencial "e" está en el rango 2,2 < e < 2,7, principalmente porque el espesor de la zona epitaxial N<sup>-</sup> debe aumentar progresivamente a medida que se desea obtener dispositivos capaces de bloquear tensiones mayores.

A consecuencia de esto, mas del 90% de la resistencia total corresponde a esta zona en los dispositivos de mayor tensión de bloqueo, lo que limita la posibilidad de producir dispositivos de II<sup>a</sup> generación capaces de operar a niveles de voltaje y potencia elevados.

La figura muestra las variaciones relativas en el aporte a la resistencia  $R_{\rm DS(on)}$  total para valores típicos de tensiones de bloqueo, ilustrando los efectos de los distintos compromisos de diseño en PowerMOSFETS de baja (50V), media (100V) y alta (500V) tensión de bloqueo construidos con la estructura básica de isla.

Importancia relativa de los distintos componentes de las pérdidas en conducción en función de la tensión máxima de bloqueo PowerMOSFETs de II<sup>a</sup> generación.

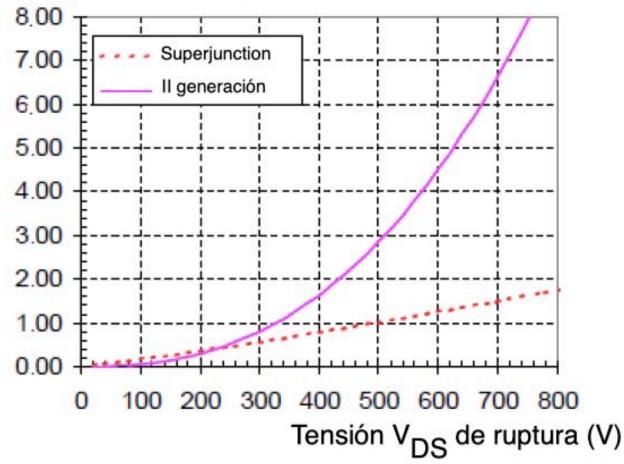

El cambio de la configuración del campo eléctrico logrado con la estructura de "Superjunction" en los PowerMOSFETs de IIIª generación se manifiesta en un cambio en la relación entre la resistencia de la zona epitaxial, R<sub>epi</sub>, y los parámetros de diseño del dispositivo, como consecuencia de lo cual el valor del parámetro "e" en la ecuación que relaciona la resistencia R<sub>DS</sub> con la tensión máxima de bloqueo de bloqueo, V<sub>BD</sub>, pasa a ser 1,3, lo que produce un aumento de la resistencia en conducción mucho mas pequeño a medida que se diseñan componentes para tensiones de bloqueo progresivamente mayores.

# Resistencia zona epitaxial (Ohm x mm<sup>2</sup>)

Relación Repi/VDS de ruptura. PowerMOSFEts de II<sup>a</sup> generación y Superjunction (III<sup>a</sup> generación). Cortesia Semikron

### ESPECIFICACIONES BÁSICAS DE UN POWERMOSFET

I.- Tensión de ruptura directa, BV<sub>DSS</sub>.

Es la tensión Drenador-Surtidor máxima que puede ser bloqueada por un MOSFET de potencia sin entrar en conducción por ruptura directa.

Dado que la estructura básica del MOSFET de potencia incluye un diodo en anti-paralelo, el dispositivo carece de capacidad de bloqueo de tensión inversa en los terminales D-S.

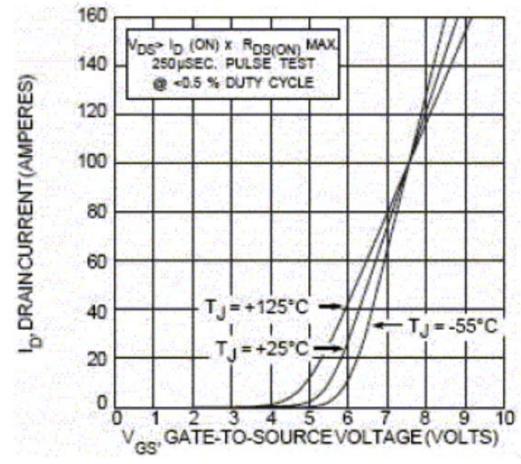

II.- Corriente Drenador-Surtidor máxima, I<sub>DSM</sub>.

Es la máxima corriente que puede ser controlada por el dispositivo sin causar fallas por sobre-calentamiento.

Esta variable es dependiente de la temperatura de juntura del transistor, y suele ser especificada para una temperatura de juntura baja, usualmente 25° y para la máxima temperatura de juntura que puede soportar el transistor que, dependiendo de los especificaciones, puede estar entre 85° y 125°. Salvo en casos especiales, el valor que se debe considerar como límite en un diseño es el especificado a la máxima temperatura.

III.- Resistencia de encendido,  $R_{DS}(on)$ .

Es la caída resistiva que aparece entre los terminales de Drenador y Surtidor cuando el dispositivo está encendido.

$R_{\rm DS}({\rm on})$  es el parámetro más importante en la definición de la capacidad de manejo de corriente del dispositivo en función de la máxima potencia disipable en una aplicación dada,  $P_{\rm DM}$ .

La potencia disipada en la juntura, P<sub>D</sub>, es:

$$P_D = I_D^2 R_{DS}$$

Luego:

$$I_{DM} = \sqrt{\frac{P_{DM}}{R_{DS}}}$$

Donde la potencia máxima disipable a una temperatura de carcasa dada está determinada por la máxima temperatura de juntura que puede soportar el dispositivo y las características térmicas del encapsulado.

Caída en conducción, V<sub>DS(on)</sub>:

$$V_{DS(on)} = R_{DS(on)}I_{DS(on)}$$

donde IDS(on) es la corriente D-S durante el intervalo de conducción.

Pérdidas en conducción P<sub>DS(on)</sub>:

$$P_{DS(on)} = V_{DS(on)}I_{DS(on)} = R_{DS(on)}I_{DS(on)}^2$$

Dada la relación exponencial entre RDS y la tensión de ruptura, el rápido crecimiento de la resistencia es un factor que limita la posibilidad de producir PowerMOSFETs capaces de operar en régimen de alta corriente y alta tensión de bloqueo.

# IV.- Transconductancia, $g_{fs}$ .

La transconductancia del MOSFET de potencia,  $g_{fs}$ , se define como:

$$g_{fS} = \frac{\Delta I_D}{\Delta V_{GS}}$$

La transconductancia depende de la temperatura de juntura y del valor de  $I_{DS}$  que este circulando.

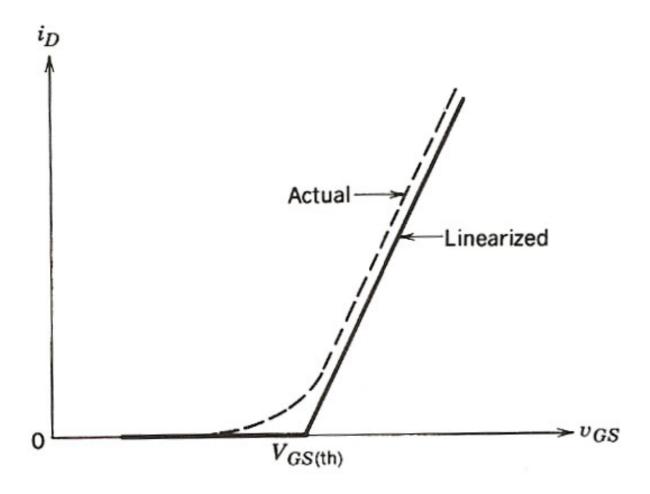

V.- Tensión de umbral.

La tensión de umbral,  $V_{GSS(th)}$ , es el valor de la tensión Compuerta–Surtidor para el cual la corriente Drenador-Surtidor empieza a ser significativa.

Es un valor convencional, definido como el punto en el cual la recta que marca la asíntota de la curva de corriente corta al eje de voltaje; define un modelo de aproximación lineal en dos trazos al comportamiento real de la relación i<sub>ds</sub> vs v<sub>gs</sub>.

Dado que los PowerMOSFETs se operan generalmente como conmutadores, para lograr la máxima capacidad de manejo de corriente y la máxima velocidad de conmutación, los circuitos de control se diseñan para que apliquen en la compuerta la máxima tensión  $v_{\rm gs}$  cuando se desea que el dispositivo conduzca, y la  $v_{\rm gs}$  mínima, cero o, preferentemente, negativa, cuando se desea apagar al dispositivo, por lo que los parámetros  $g_{\rm fs}$  y  $V_{\rm GSS(th)}$  no suelen ser de interés para el diseñador de aplicaciones de Electrónica de Potencia.

Relación real entre  $I_D$ ,  $V_{gs}$  y  $V_{GSS(th)}$ .

Relación real típica (a trazos interrumpidos) y aproximada a trazo continuo entre  $I_{\text{D}}, \ V_{\text{gs}}$  y  $V_{\text{GSS(th)}}.$

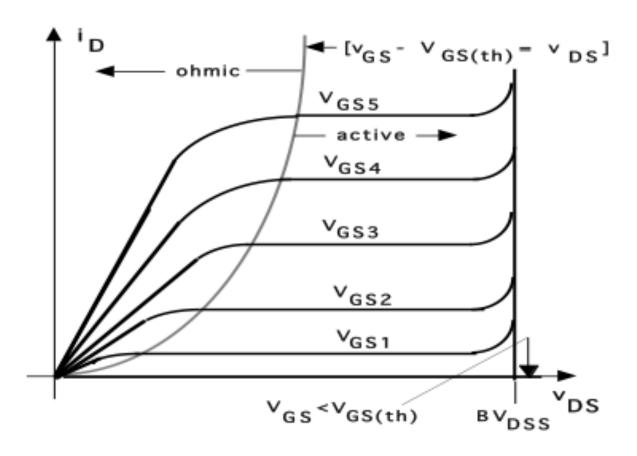

ZONAS DE OPERACIÓN DE UN POWERMOSFET.

Características corriente/voltaje ideales en un transistor de efecto de campo de potencia (PowerMOSFET)

En principio un PowerMOSFET tiene, como todo MOSFET, un área V/I de operación dividida entre una región óhmica, en la que la relación entre la corriente  $i_{DS}$  y el voltaje  $V_{DS}$  está definida por el valor de la resistencia  $R_{DSon}$ , y una zona "activa" o "saturada", en la cual el valor  $i_{DS}$  es constante y depende solamente de la tensión  $V_{gS}$ .

En la práctica la potencia disipada si el PowerMOSFET operase de modo estacionario en la zona activa sería tan alta que el dispositivo se sobrecalentaría y resultaría destruido en muy corto tiempo, por lo que el PowerMOSFET solo puede operar como un conmutador, que solo puede operar en forma estacionaria en el estado de corte o en la zona óhmica.

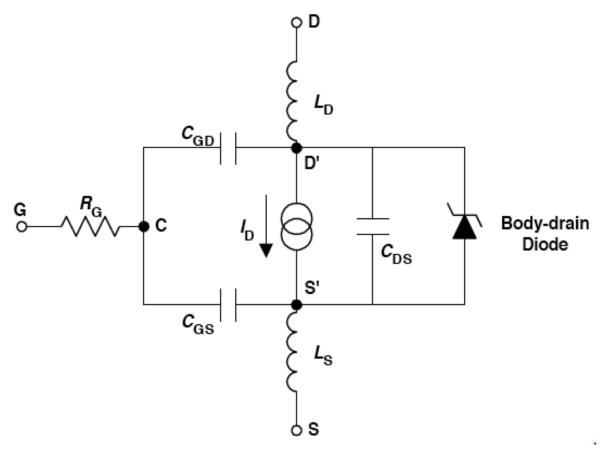

# MODELO EQUIVALENTE BÁSICO DEL POWERMOSFET

Modelo equivalente del PowerMOSFET para analizar los procesos de conmutación con carga inductiva.

En el modelo las inductancias  $L_{\rm D}$  y  $L_{\rm S}$  son, respectivamente, las inductancias parásitas debidas al cableado interno de conexión de las metalizaciones de Drenador y Surtidor a los respectivos contactos en la carcasa de montaje,

Rg es la resistencia de la conexión de compuerta (Gate).

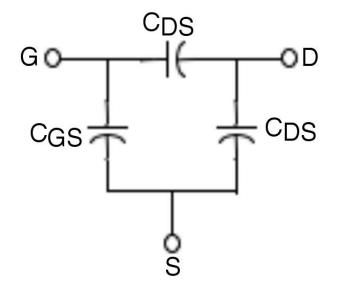

Las capacitancias del modelo son:

- 1.- Capacitancia Compuerta-Surtidor, C<sub>GS</sub>.

- 2.- Capacitancia Compuerta-Drenador, C<sub>GD</sub>.

- 3.- Capacitancia Drenador-Surtidor, C<sub>DS</sub>.

En general las tres capacitancias dependen de la geometría del dispositivo y son independientes de la temperatura de juntura.

Adicionalmente, los valores de las capacitancias  $C_{GD}$  y  $C_{DS}$  son función de las tensiones  $V_{DS}$  y  $V_{GS}$ , y de la frecuencia de conmutación.

C<sub>GS</sub> es básicamente constante.

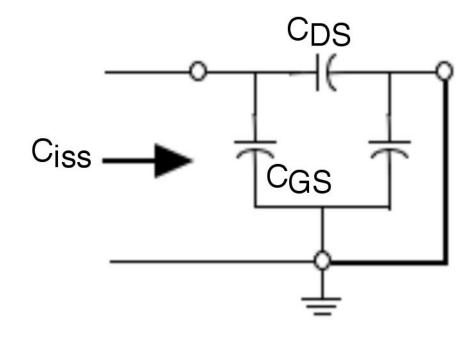

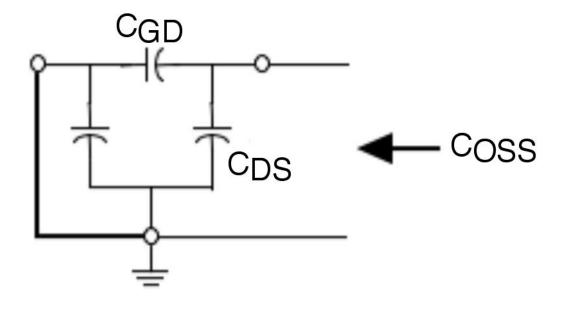

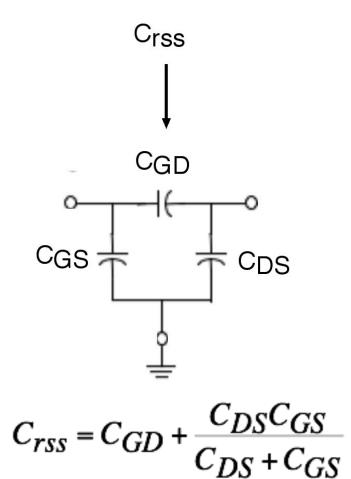

Usualmente el fabricante no especifica directamente los valores de las capacitancias del modelo, sino los de las tres capacitancias que son directamente medibles desde los terminales del dispositivo:

$$C_{iss}$$

,  $C_{oss}$  y  $C_{rss}$ .

Con estos valores se tiene así un sistema de tres ecuaciones con tres incógnitas, las capacidades del modelo, que pueden por lo tanto ser calculadas en función de las capacitancias medibles entre los terminales del dispositivo.

Las relaciones entre las capacitancias especificadas y las del modelo son las siguientes:

$$C_{iss} = C_{GS} + C_{GD}$$

$$C_{oss} = C_{DS} + C_{GD}$$

# VII.- Tiempos de conmutación.

Las conmutaciones del MOSFET de potencia están controladas los proceso de carga y descarga de las tres capacidades del modelo, y en las especificaciones queda caracterizado por el fabricante con los siguientes tiempos, definidos para una señal de control aplicada entre los terminales Compuerta-Surtidor de muy alta velocidad de subida y bajada (usualmente 50ns), cuando el PowerMOSFET esta conectado en un circuito con una tensión de alimentación constante, controlando una carga inductiva en una configuración con diodo de libre conducción de alta velocidad de conmutación (idealmente un diodo Schottky).

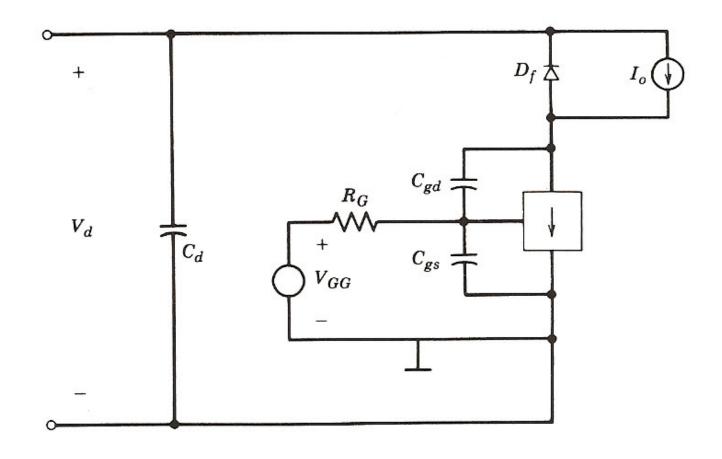

Circuito de prueba usado para medir las características de conmutación con carga inductiva.

Formas de onda de interés durante el encendido del PowerMOSFET.

#### A.- Encendido.

Se asume que existe la corriente de carga en su valor nominal, corriente que está circulando en el lazo cerrado carga-diodo de libre conducción en el momento en el cual se aplica la señal de encendido en la compuerta del PowerMOSFET.

El proceso de encendido comprende los siguientes intervalos:

1.- Tiempo de retardo de encendido,  $t_{d(on)}$ . Concluida la subida del pulso de control de encendido, que se asume instantánea, se va cargando la capacitancia de juntura  $C_{GS}$  y el voltaje GS sube hacia el valor de umbral de conducción,  $v_{GSth}$ . En este intervalo no hay cambios observables en la corriente o la tensión D-S.

2.- Tiempo de alza,  $t_r$ . Es el tiempo que transcurre desde que el voltaje GS llega el nivel de umbral,  $v_{\rm GSth}$ , hasta que la corriente  $I_{\rm D}$  alcanza su valor final. Una vez alcanzado su nivel de umbral la tensión G-S permanece esencialmente constante hasta el final del proceso de encendido.

El tiempo de alza se divide en tres sub-intervalos:

- a.-Tiempo de subida de la corriente D-S, t<sub>ri</sub>: En este sub-intervalo la corriente de Drenador crece rápidamente hasta el valor de la corriente de carga externa, pero el voltaje Drenador-Surtidor no cambia ya que el diodo de libre conducción esta conduciendo, lo que mantiene la tensión de Drenador fija al voltaje de alimentación del circuito.

- b.-Primer tiempo de bajada del voltaje D-S  $t_{vf1}$ : Cuando la corriente de Drenador alcanza el valor de la corriente de carga el diodo de

libre conducción deja de conducir y el voltaje de Drenador cae rápidamente. Usualmente este proceso termina cuando la tensión DS alcanza un valor aproximado al 10% del inicial.

- c.-Segundo tiempo de bajada del voltaje t<sub>vf2</sub> (tiempo de cola): La tensión de Drenador sigue reduciéndose pero con una pendiente de caída significativamente menor.

- 3.-Final del proceso: la tensión Drenador-Surtidor se estabiliza en su valor final, y el voltaje Compuerta-Surtidor sube hasta el valor final fijado por la tensión externa y el arreglo de las capacitancias del MOSFET de potencia.

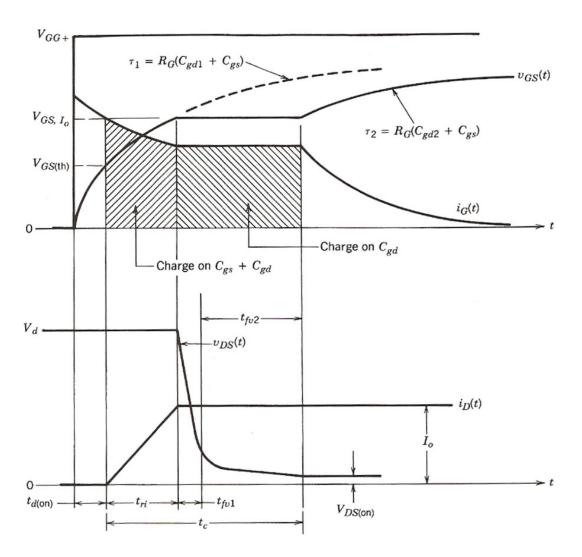

Circuitos equivalentes aplicables durante las distintas etapas del encendido. a) intervalo  $t_{d(on)}$ , b) intervalo  $t_{ri}$ , c) intervalo  $t_{fv1}$ , d) intervalo  $t_{fv2}$ .

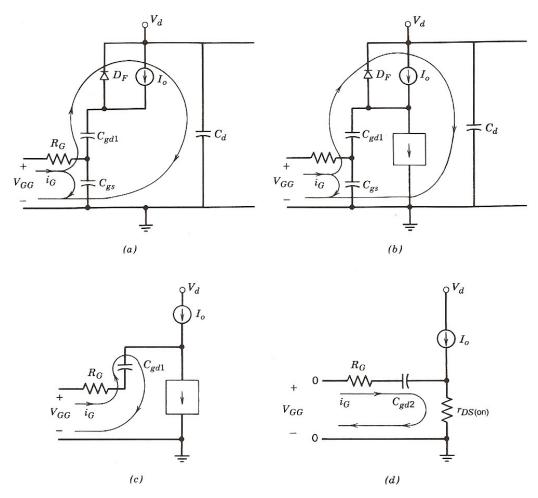

Formas de onda de interés durante el apagado, con un diodo de libre conducción ideal.

## B.- Apagado.

Por hipótesis se considera que la corriente DS está estabilizada al nivel de la corriente nominal de carga en el instante en que termina el pulso de encendido del PowerMOSFET, y que en paralelo con la carga está conectado un diodo de libre conducción de alta velocidad, preferiblemente tipo Schottky.

El proceso de apagado se cumple en las siguientes etapas:

1.-Tiempo de retardo de apagado,  $t_{d(off)}$ . Terminado el tiempo de caída de la señal de control aplicada a la compuerta, que se considera instantánea, se empieza a extraer la carga del condensador equivalente de entrada y la tensión  $v_{GS}$  comienza a reducirse; en este intervalo no ocurren cambios apreciables en la corriente ni en la tensión DS.

2.- Tiempo de caída,  $t_f$ . Es el tiempo que transcurre desde que el voltaje DS empieza a subir hasta que la  $I_D$  alcanza el valor final de cero.

Este tiempo se divide en los siguientes sub-intervalos:

- a.-Primer tiempo de subida de voltaje, t<sub>rv1</sub>: La tensión Compuerta-Surtidor se estabiliza, la corriente de Drenador permanece constante y la tensión Drenador-Surtidor empieza a subir lentamente hacia su valor final.

- b.-Segundo tiempo de subida de voltaje,  $t_{rv2}$ : Cambia la pendiente de variación de la tensión Drenador-Surtidor que sube rápidamente hacia su valor final.

3.-Tiempo de caída de corriente,  $t_{\rm fi}$ : La tensión Drenador-Surtidor alcanza su valor final, la tensión Compuerta-Surtidor vuelve a descender hacia cero; la corriente de Drenador cae y alcanza el valor cero cuando la tensión Compuerta-Surtidor cruza descendiendo el valor del umbral de conducción ( $v_{\rm GSth}$ ).

VIII.- Área de operación segura (SOA).

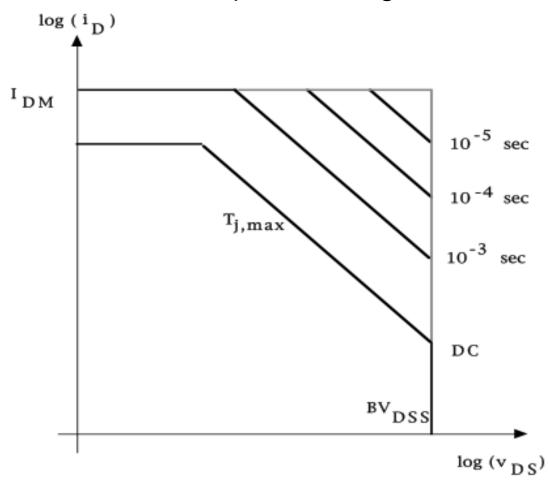

Área de operación segura (SOA) de un PowerMOSFET típico.

En los MOSFET de potencia el área de operación segura esta limitada por la máxima corriente Drenador-Surtidor, el voltaje de ruptura Drenador-Surtidor y la hipérbola de máxima disipación, y no existe el fenómeno de ruptura secundaria.

El área de operación segura estable está limitada por la corriente l<sub>DS</sub> que puede ser aceptada por el dispositivo en régimen estacionario; por encima de este valor se indica el límite transitorio, que corresponde al valor máximo de la corriente pulsante, que puede ser empleado en operaciones de conmutación rápida, y también para fijar el punto de disparo de la autoprotección contra fallas por sobre-corriente.

La señal de autoprotección debe de ser capaz de apagar al PowerMOSFET en un tiempo menor al especificado como duración máxima del pulso de sobre corriente.

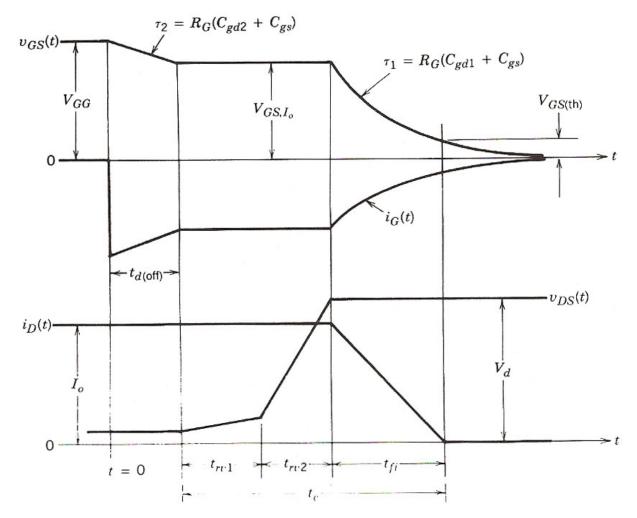

## IX.- FALLAS DE CONMUTACIÓN.

La inevitable existencia de elementos parásitos en la estructura del PowerMOSFET puede causar fallas tanto durante el proceso de encendido como el del apagado; en general los fabricantes procuran optimizar sus componentes para evitar estos problemas, pero siempre deben tomarse precauciones en el diseño de los circuitos de aplicación.

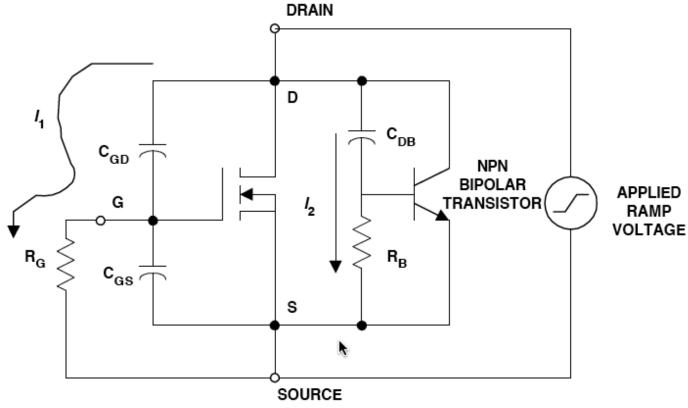

I.-Encendido no deseado.

Existen dos posibles mecanismos para producir un encendido accidental del PowerMOSFET por exceso de dV<sub>D</sub>/dt:

Circuito equivalente a considerar para determinar la posibilidad de aparición de una falla en encendido por variación rápida de la tensión entre los terminales principales del PowerMOSFET, mostrando los dos caminos de encendido  $(I_1, I_2)$ .

1.- Por ruido generado en la resistencia Compuerta-Surtidor

Todo cambio en la tensión externa aplicada a los terminales DS produce también un cambio en la tensión DG, lo que requiere que circule una corriente a través del condensador GD y de la resistencia externa Compuerta-Surtidor (R<sub>G</sub>). Esta corriente produce una tensión positiva en el terminal de compuerta que, de alcanzar un valor suficiente, puede producir el encendido indeseado del dispositivo.

La tensión  $v_{gs}(t)$  producida por la aplicación de una variación de tensión en los terminales principales es:

$$v_{gs}(t) = i_1(t)R_G = R_G C_{GD} \frac{dv_{DS}(t)}{dt}$$

Y el valor del dv/dt crítico capaz de producir el encendido indeseado del PowerMOSFET  $\frac{dv_{DS}(t)}{dt}$  es:

$$\frac{dv_{DS}(t)}{dt}\Big|_{MAX1} = \frac{V_{gsth}}{R_G C_{GD}}$$

2.- Por encendido indeseado del BJT secundario.

Todo cambio en la tensión externa aplicada a los terminales DS produce también un cambio en la tensión del condensador parásito DB, lo que requiere que circule una corriente a través del mismo y de la resistencia interna R<sub>B</sub>, que es la resistencia de base del transistor BJT NPN secundario.

Esta corriente produce una tensión positiva que, de alcanzar un valor suficiente, puede producir el encendido del transistor parásito, y por lo tanto el encendido indeseado del dispositivo.

Tensión  $v_{be}(t)$  producida por la aplicación de una variación de tensión en los terminales principales:

$$v_{be}(t) = i_2(t)R_B = R_B C_{DB} \frac{dv_{DS}(t)}{dt}$$

De donde, el valor del dv/dt crítico capaz de producir el encendido indeseado del PowerMOSFET,  $\frac{dv_{DS}(t)}{dt}\Big|_{MAX2}$ , es:

$$\left. \frac{dv_{DS}(t)}{dt} \right|_{MAX2} = \frac{V_{beth}}{RBC_{DB}}$$

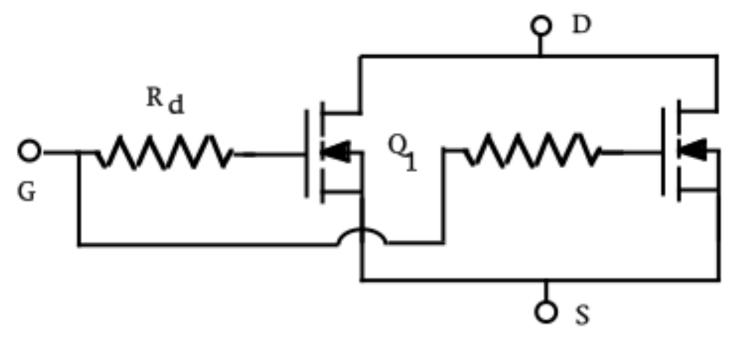

## X.- CONEXIÓN DE POWERMOSFETS EN PARALELO.

Esquema de conexión de PowerMOSFETs en paralelo.

Al no existir el peligro de la corrida térmica, PowerMOSFETs del mismo tipo pueden conectarse directamente en paralelo. Las impedancias del circuito de control deben ajustarse para asegurar conmutaciones simultáneas.

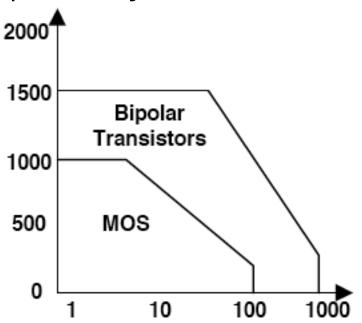

## XI.- OMPARACIÓN ENTRE POWERMOSFET Y BJTs DE POTENCIA.

Asumiendo dispositivos implementados con la tecnología de Si, en chips de la misma superficie y encapsulados en carcasas del mismo tipo, los resultados de una comparación entre BJTs y PowerMOSFETs diseñados para operar con la misma tensión de bloqueo y la misma corriente máxima son los siguientes:

- 1.-Ventajas de los PowerMOSFETs sobre los BJTs:

- 1.- La conmutación de los PowerMOSFETs es órdenes de magnitud mas rápida.

- 2.- Los PowerMOSFETs pueden ser conectados directamente en paralelo.

- 3.- El control de la conmutación por voltaje de Compuerta en los PowerMOSFETs permite que los circuitos de control de los PowerMOSFETs sean mas simples y mucho mas eficientes que los circuitos de control por corriente de base de los BJTs.

- 4.- Los PowerMOSFETs tienen un diodo de conducción inversa intrínseco en su estructura, lo que simplifica en muchos casos su uso en circuitos conversores DC/DC y DC/AC.

- 2.-Ventajas de los BJTs sobre los PowerMOSFETs:

- 1.- Para un mismo nivel de corriente las pérdidas en conducción son mas elevadas en los PowerMOSFETs.

- 2.- Las pérdidas en conducción en los PowerMOSFETs aumentan cuando se trata de aumentar la tensión de bloqueo.

Comparación entre las capacidades voltaje/corriente de BJTs de potencia y PowerMOSFETS.

Escala vertical: voltaje de bloqueo máximo Escala horizontal: corriente máxima.

La gráfica combina las capacidades de los PowerMOSFETS de II<sup>a</sup> y III<sup>a</sup> generación.